本文要點

降低 CPU 或 GPU 功耗的技術有許多,這些技術聚焦軟體/韌體層面、系統層面和電晶體架構層面 |

|

其中兩種降低功耗的技術為:動態電壓和頻率調節,即調整電源電平、信號電平和時鐘頻率以回應功耗需求 |

|

作為低功耗 VLSI (VLSI,超大型積體電路) 的一部分,動態電壓和頻率調節技術必須在硬體層面上實現 |

高速處理器使用動態電壓和頻率調節來調整功耗

當今的 CPU 能夠處理的資料量比以往任何時候都要多,這要歸功於摩爾定律的擴展和對更高級應用的需求不斷增長。 2000 年 Intel 預測,如果按照線性推斷,CPU 擴展將最終增加總功耗,直到超過太陽的總輸出功率。當時,降低 CPU 功耗的方法和低功耗架構成為 CPU 設計工程師和製造商的主要關注點,這種趨勢一直持續至今。

低功耗 CPU、GPU、FPGA 和 MCU 設計方法主要集中在三個方面:

低功耗架構: |

|

軟體和韌體: |

|

節流和睡眠模式: |

其中,對於開始分析元件資料表的系統設計工程師來說,最後一個方面可能最為突出。動態電壓和頻率調節是主要的用於限制時鐘頻率和控制複雜處理器功耗的方法,本文將詳細介紹這二者是如何影響設計的。

動態電壓和頻率調節的工作原理

當下的現代數位元件由基於 MOSFET 的電路構成,這些電路主要採用 CMOS 工藝生產;儘管在市售元件中仍然可以找到 TTL、ECL、NMOS 和 BiCMOS 邏輯系列。所有基於 MOSFET 的數位邏輯電路都使用電壓電平來表示邏輯狀態,而邏輯電平必須位於某個數值範圍內,以表示二進位邏輯中的 1 或 0。該電壓的大小取決於數位元件的電源電平。

在處理器中,我們有多個區塊來執行與處理和傳輸數位資料有關的不同功能。其中包括:

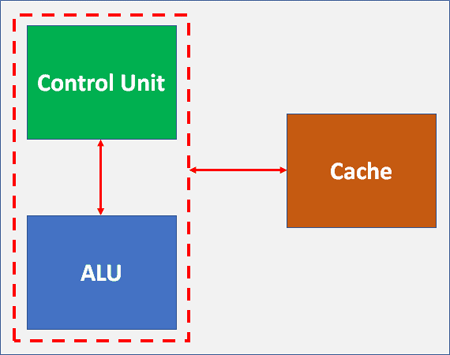

CPU 區塊圖

緩存 (Cache): |

|

控制單元 (Control unit): |

|

算數邏輯單位 (ALU): |

最後是內核,用於接收並執行控制單元提供的指令。現代 CPU 可能有多個內核 (以 2 的冪次方為單位) ,以此實現應用並行化。每個內核使用控制單元提供的輸入資料和邏輯指令來執行特定的資料操作。在內核和各個邏輯單元內,可以應用動態電壓和頻率調節來降低總功耗。

邏輯單元中電晶體的電壓電平

電晶體在工作時會在高電壓電平和低電壓電平之間切換。儘管我們喜歡把電晶體看作是理想的元件,但它們會有我們不希望出現的寄生效應,這決定了它們在工作中的切換方式。下圖顯示的是一個包含寄生效應的 MOSFET 等效電路圖。

輸入元件之間帶有寄生電容的等效 MOSFET 模型

在這個例子中,我們有一個涉及三個電容與一個整流半導體元件並聯的三角電路。每個節點上的電容完全是預料之外的,是由於現代 MOSFET 的緊湊性質而產生的。這些寄生電容值源自積體電路中的導線結構,即耦合電容。請注意,我們沒有包括引線上的電感,因為它在小型電晶體中可以忽略不計。

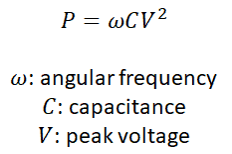

當切換邏輯電路中的 MOSFET 時,電容電荷就會流入上述電路,對這些電容進行充電/放電。然後,總的等效電容決定了 MOSFET 切換狀態所需的時間 (即,就像在 RC 電路中一樣) 。切換過程中的功耗是:

切換 MOSFET 所需的功耗

從這個公式中,我們可以看到,電晶體可以在較低的電壓下運行,以減少功耗。矽片上的電容是非線性的,電容大致與電源電壓成反比。在較低電壓下運行,切換時間也隨之增加,然後切換信號的功率頻譜就轉移到了較低的頻率。

時鐘頻率

CPU 內核包含一個時鐘,它以高度穩定的參考振盪器 (如晶體) 產生的某個頻率的特定倍數運行。相環鎖定迴路 (PLL) 用於根據這個參考時鐘產生一個或多個更快或更慢的時鐘。透過降低時鐘速度,電晶體的切換速度變慢,這也降低了 CPU 的功耗。如果內核電壓不變,那麼每個時鐘週期的功耗是不變的,但在給定的時間間隔內的總功耗較低。

優化設計軟體中的操作模式

可以使用IC設計軟體中的一套標準設計庫,在低功耗 VLSI 中實現動態電壓和頻率調節。雖然達到設計收斂所需的時間較長,而且產品變得更加複雜,但這種投資物有所值,因為這可以降低功耗。想要在產品中實現動態電壓和頻率調節的設計工程師需要考慮所需的操作模式,並確定在操作過程中關閉哪些核心功能。

利用業界一流的 VLSI 設計軟體、系統分析工具和電路模擬器,可以最大限度地降低整個系統的功耗,而不僅僅是 CPU 內核的功耗。如果您需要在實現動態電壓和頻率調節的同時完成積體電路的設計、模擬和佈局,Cadence 的系統分析工具可以提供全面的電路、IC 和 PCB 設計工具套件,幫助您輕鬆駕馭任何應用和複雜程度。

而 Cadence 最新一代 SI/PI 解決方案 Sigrity™ X,以能進行系統級分析的強大新模擬引擎為特色,並包含 Cadence Clarity™ 3D Solver 的創新大規模分散式結構,更可解決當今頂尖技術人員在 5G 通訊、汽車、超大型規模運算以及航太與國防產業,所面臨到的系統級模擬規模與可擴展性挑戰。

Sigrity 最新版本已於日前發佈,想了解新版本中有那些實用功能?

歡迎填寫下表索取由映陽科技編寫的 「 What’s New in Sigrity 2021.1」圖文詳解中文版。

欲進一步了解更多 Cadence 系統分析工具應用,亦歡迎聯繫 Cadence 台灣授權代理商 - 映陽科技團隊。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」