本文翻譯、轉載自 2019 年 9 月發佈於 Signal Integrity Journal 的文章《 On-Board Decoupling Capacitor Optimization 》。

電源完整性(PI)分析的目的是確保系統中所有晶片供電充足且穩定。隨著印刷電路板日益複雜、系統尺寸持續減小,確保關鍵晶片的電源穩定變得越來越重要。設計階段儘早優化其位置和數值將降低後期設計變更或電路板重新設計的風險。透過將電源網路的阻抗保持在特定目標 [1] 以下,可以確保關鍵晶片的供電穩定。

去耦電容可以在一定頻率範圍內降低阻抗,且這種方法成本較低。選擇板載去耦電容來優化電源層的阻抗時,需要考慮許多參數 [2]。為了將電源層的阻抗降至安全目標以下,不僅要考慮電容的數量和位置,還要考慮電容量、等效串聯電感(ESL)、等效串聯電阻(ESR)以及安裝電感。

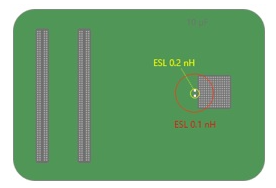

以上許多參數都可以簡化為電容的「有效半徑」這一指標 [3]。有效半徑是指電容周圍可有效減小電源波動的近似半徑。有效半徑隨頻率而變化,而且ESL增加時會顯著減小(圖1)。

圖 1:10 µF 電容在 ESL 為 0.1 nH 時的有效半徑(紅色圓圈)與 ESL 為 0.2 nH 時的有效半徑(黃色圓圈)。

頻率為 15 MHz。

電源網路的佈局改變會導致板載去耦電容的回路電感發生較大變化。判斷去耦電容在降低電源網路阻抗的有效性時,晶片電源引腳與電容之間的回路電感量是一個關鍵指標。此外,透過回路電感來優化去耦電容的配置可降低電源網路的阻抗並提高電源分配網路(PDN)的穩定性,而且這種方法毫無成本。

針對 DDR-4 設計中去耦電容的配置和選擇,下圖展示了一個快速優化過程,該設計包括一個帶有兩個菊輪鍊式雙列直插存儲模組(DIMM)的存儲控制器。佈局之後,需要快速分析並向 layout 工程師回饋。我們透過混合求解器,利用二維自我調整有限元網格化方法來分析去耦電容變化的影響。我們的分析針對 20 MHz 以下,在這種頻率下,PCB 設計中使用的表面貼裝電容元件的阻抗會有很大作用。

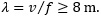

在這樣的頻率下,電磁場的波長是 。這個波長是根據電磁場的速度

。這個波長是根據電磁場的速度  計算所得,其中: c 是空氣中的光速,假定相對介電常數

計算所得,其中: c 是空氣中的光速,假定相對介電常數 ,這一常數在基於 FR-4 的設計中較普遍。這個波長明顯大於我們考慮的 PCB 設計尺寸,因此准靜態近似成立,而且我們的模擬可以為電路板設計團隊提供快速回饋。

,這一常數在基於 FR-4 的設計中較普遍。這個波長明顯大於我們考慮的 PCB 設計尺寸,因此准靜態近似成立,而且我們的模擬可以為電路板設計團隊提供快速回饋。

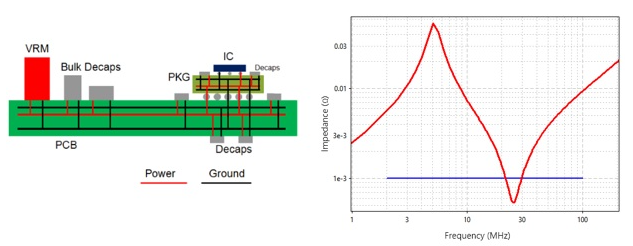

圖 2 顯示了一個 PCB 的剖視圖,其中有一個晶片,由單個電源網路供電。圖中顯示了影響電源網路的多種去耦電容,包括電壓調節模組(VRM)附近的儲能電容、晶片附近的表面貼裝電容以及封裝內嵌的片載電容。這些不同類型的電容可降低不同頻率範圍內的電源網路阻抗。在此,我們將重點關注IC附近表面貼裝電容的配置,因為電路板設計團隊在這些電容的配置和選擇上通常有相當大的靈活性。

圖 2 左圖:VRM 供電 IC 的典型電源網路佈局的剖視圖。電源網路透過其封裝(PKG)為 IC 供電。右圖:佈局後的 DDR-4 設計中存儲控制器 IC 的電源網路阻抗(紅色)與目標阻抗(藍色)的對比。資料來源:[4]

注意 DDR-4 存儲控制器晶片上電源網路的阻抗,可發現它在許多頻率下都超過了目標阻抗(圖 2 右圖)。該設計已經佈局完成,電源網路上有 100 多個去耦電容,但在某些頻率下,阻抗仍超出目標阻抗 10 倍以上。實現目標阻抗可以將電源網路上的雜訊容限保持在安全範圍內。當電源網路阻抗大幅超過目標值時,任何瞬態電流雜訊都會導致與電源網路相連的所有晶片的電壓雜訊達到危險水準。在這種 DDR-4 設計上改善電源網路阻抗將大大降低因存儲控制器晶片上的雜訊而進行重新設計的風險。

首先類比去耦電容與晶片引腳之間的回路電感,從而分析去耦電容在電路板上的配置。為進行這種分析,混合模擬器會在晶片的電源引腳上創建一個測量埠,並將電容短路,這樣計算出的回路電感只跟電路板的佈局有關。根據這一分析,我們發現電源網路上有四個去耦電容遠離晶片。而電路板上有足夠的空間讓其中的兩個電容距離晶片。這一簡單改變便可降低電源網路的阻抗,從而在不增加製造成本的情況下更接近目標阻抗(圖4)。

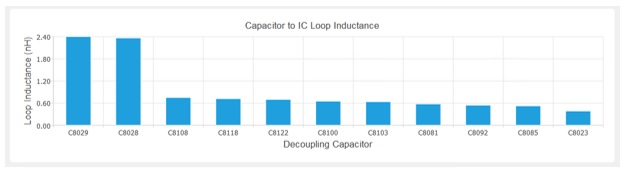

我們針對 10 個完整設計分析了晶片與去耦電容之間的回路電感。透過測量電源平面的回路電感,發現半數以上的設計都存在無效的電容配置。例如,分析某個完整設計中 12V 電源網路上一個元件與所有去耦電容之間的回路電感時,發現其中兩個電容的回路電感比電源網路上其他電容大五倍(圖3)。

這些電容的配置使其不起作用,而電源網路上這些器件的高回路電感使其更容易在高密度的電路板設計中產生或吸收雜訊。這意味著它們在電路板上的存在基本無用,實際上還會對附近敏感的信號網路造成損害。

圖 3:完整設計中 12V 電源網路上晶片與去耦電容之間的回路電感。從圖中可以看到,電源網路上兩個電容 C8029 和 C8028 的回路電感幾乎是其他電容的五倍。

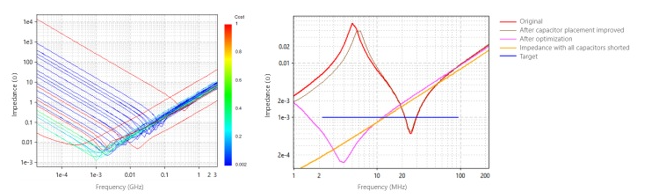

回到之前的 DDR-4 設計,接下來我們分析設計中的電容數量和類型優化。圖 4 的左圖中是優化過程中使用的不同電容模型。優化時在不到 30 分鐘的時間內分析了該設計中配置的 100 多個去耦電容,得到的結果在 10MHz 以下低於目標值。可以看到,即使所有電容都對地短路,10 MHz 以上時電源網路的阻抗也會高於目標阻抗(圖 4 右圖)。

最終方案中的電容數量與原始設計相同,但可以實現明顯更低的電源網路阻抗。儘管完整的電源分配網路分析還應包括與 VRM 連接的儲能電容以及封裝內去耦電容,但它們分別在較低和較高頻率下作用最大。圖中展示的都是與板載表面貼裝電容相關度最高的頻率範圍。

圖 4 左圖:最終優化時使用去耦電容的阻抗模型。每條線都代表一個電容,線的顏色表示色條中標明的電容成本。

圖 4 右圖:相比目標阻抗(藍色),存儲控制器晶片在不同頻率下的電源網路阻抗。紅色代表初始的佈局後的設計、淺棕代表通過電容器配置優化降低回路電感後的設計、粉色代表優化後的設計、橙色表示所有電容短路後的阻抗。

[1] Smith, L. D. and Bogatin, E. Principles of Power Integrity for PDN Design Simplified. Prentice Hall, 2017. pp 10-12.

[2] Novak, I. “Comparison of Power Distribution Network Design Methods: Bypass Capacitor Selection Based on Time Domain and Frequency Domain Performances.” TecForum MP3, DesignCon 2006.

[3] Chen, Huabo, Jiayuan Fang, and Weimin Shi. "Effective decoupling radius of decoupling capacitor." IEEE 10th Topical Meeting on Electrical Performance of Electronic Packaging. IEEE, 2001.

[4] Team-based PDN Design with PowerTree, PowerDC, and OptimizePI Rapid Adoption Kit. http://support.cadence.com 2017.

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」