By Paul McLellan, Cadence

PCIe 起源

PCIe (Peripheral Component Interconnect Express,週邊元件快速互連) 是早期 PCI 匯流排的升級版。PCI 由 Intel 開發,於 1992 年問世。它取代了幾種陳舊的、速度較慢的匯流排,這些匯流排在早期的 PC 中以某種特殊的方式使用。PCI 主要是 32 位元的匯流排,但是也支援 64 位。最重要的一點是,PCI 是一種平行匯流排。如今,PCI 只具有歷史意義,我們已經不再使用,所以在此就不再贅述。

2004 年,一群 Intel 工程師組建了 Arapaho 工作組,開始開發新的標準。後來,其他公司也逐漸加入了這個小組。該標準經過幾次更名,最後才確定為 PCI Express (PCIe)。在某些方面,PCIe 是 PCI 的繼承者,因為它們的功能類似。在其他方面,PCIe 是一種完全不同類型的設計。尤其特別的是,PCIe 是一種串列匯流排,比起 PCI 的老式平行介面 (以及那個時代幾乎所有的其他匯流排),它更像一個板載網路。

PCIe 標準的進化

最初的標準是 PCIe 1.0a,每通道資料速率為 250MB/s,總速率達到 2.5GT/s (每秒傳輸千兆bits)。與其他串列匯流排一樣,它的性能也通常以每秒傳輸量來衡量,以避免將附加位元算作「資料」。PCIe 1.0a 使用 8b/10b 編碼方案,因此只有 80% 的傳輸位元是真正的「資料」。

附加位元主要有兩個功能 :

首先,它們確保始終有足夠的時脈過渡供序列介面恢復時脈。

第二,它們可以確保沒有淨直流電流。

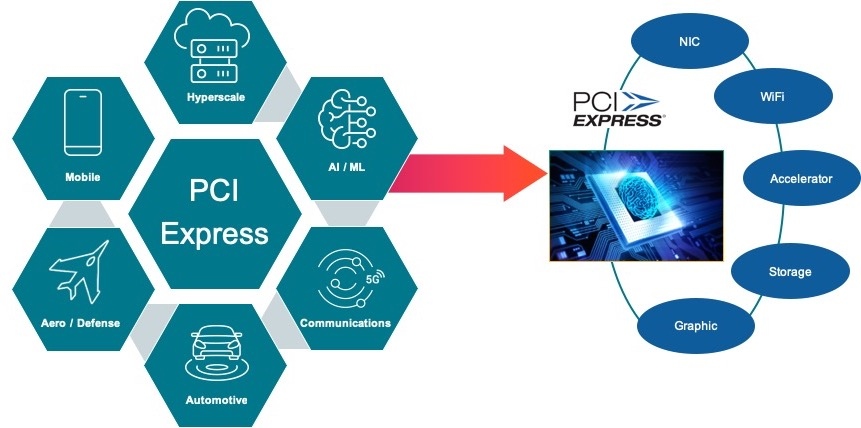

之後,該標準定期進行升級,傳輸速率更高。由於 PCIe 主要用於基於Intel處理器的 PC 和伺服器上,實際上,在Intel發佈使用 PCIe 的處理器之後,新標準就開始生效了。標準演進的總體理念是挑選在當時的主流工藝節點上可以實現的傳輸速率。然而,PCIe 的應用非常普遍,因此無論底層架構如何,在大多數需要高性能外設匯流排的設計中,都會用到 PCIe。例如,在 Arm 伺服器基礎系統架構規範中就規定了 PCIe 的要求。

2007 年推出的 PCIe 2.0 將傳輸速率提高了一倍,但沿用了相同的編碼方案。

2010 年推出的 PCIe 3.0 改用了效率更高的 128b/130b 編碼方案,並增加了已知二進位多項式的加擾功能,以在 0s 和 1s 的時脈恢復之間取得良好平衡,而且沒有直流偏置。這也顯著提高了傳輸速率。一個 16 通道的 PCIe 3.0 介面的傳輸速率達 15.7GB/s。但實際上,如果一個設計需要這樣的頻寬,那麼升級到 PCIe 4.0 會更加輕鬆。如今,PCIe 3.0 是出貨設備中部署最廣泛的 PCIe 版本。例如,Google TPU 3 中使用的是 PCIe 3.0,而目前的 USB4 標準也是基於 PCIe 3.0。PCIe 從標準獲得批准到成為主流,花費了近十年的時間——這一點聽上去可能有點令人震驚。這與信用卡的採用過程如出一轍:在很多人擁有信用卡之前,商家因為麻煩不願意接受信用卡支付,而在很多商家接受信用卡支付之前,人們也不願意擁有信用卡。

PCIe 4.0 保留了相同的 128b/130b 編碼方案,但傳輸速率再次翻倍,達到 16GT/s。Cadence 提供符合 PCIe 4.0 的 IP。PCIe 的另一個重要方面是,其他協議是建立在基本傳輸機制和 PHY 上的。CXL 也搭載了 PCIe。從這些可以看到,PCIe 4.0 是當前設計的主流。Intel 的 Tiger Lake 移動處理器支援 PCIe 4.0,AMD 的 Zen2 CPU 系列也是如此。這使得它對任何一種外設晶片都很有吸引力,比如 SSD 控制器或網路,然後由於連鎖反應,它對其他非 x86 系統也很有吸引力。

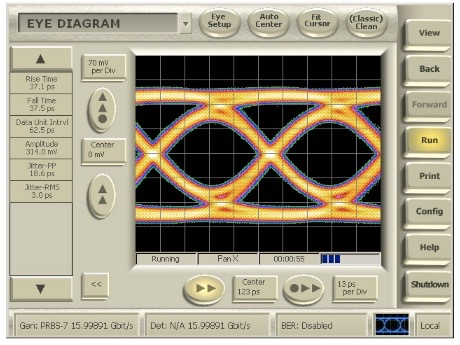

PCIe 5.0 的設計工作已經開始 (標準在 2019 年 5 月獲得批准),性能為 32GT/s。此外,人們還對 PCIe 6.0 (最終標準尚未獲得批准) 感興趣,其性能為 64GT/s,並改用了 PAM4 信令,提供四個電壓水準,因此每個時脈週期有兩個比特 (bits)。自從 Cadence 在 112G SerDes 中開始使用 PAM4 信令以來,我們已經積累了豐富的經驗,詳情參閱文章《DesignCon 論文下載 | 如何實現 112G SerDes 的信號完整性》。

從設計和 IP 的角度來看,它是主流,所以本文的其餘部分將集中關注 PCIe 4.0 和 5.0 版本 (並稍微探討未來的 6.0 版本)。

主流版本:PCIe 4.0、5.0 和 6.0 版本應用

隨著越來越多的系統升級,市場上也有越來越多的產品上市,PCIe 5.0 的應用正在加速。話雖如此,PCIe 3.0 和 4.0 仍然是目前最成熟的 PCIe 介面,作為各種 I/O 用例的主要互連形式,被廣泛部署在大量的應用中。正如前文所說,PCIe 6.0 的時代即將到來,並且很多人都對此抱有期待。

顯然,在某種程度上,每一代 PCIe 都有更高的性能,但這不僅僅體現在資料表上表現突出的數位上——更可以實現更強大的應用:

對於乙太網來說,PCIe 4.0 可以用於 100G 和 200G。PCIe 5.0 可將其性能提升到 400G,目前已經可供使用。而在未來,PCIe 6.0 將把這一數位提升到 800G。 |

|

對於固態硬碟 (SSD) 來說,PCIe 4.0 可以使傳輸速率達到約 7000MB/s,PCIe 5.0 將其提升到約 14GB/s,而 PCIe 6.0 應該會將其進一步提升到 28GB/s。 |

|

人工智慧 (AI) 和 機器學習 (ML) 需傳輸海量資料,PCIe 介面造成了瓶頸。幾乎所有的應用都是如此,比如自動駕駛、醫療成像、基因組測序、資料採擷等等。無論是在 CPU、GPU、FPGA,還是在 ASIC/SoC(如 Google 的 TPU)上進行訓練/推理,瓶頸都是 PCIe。 |

|

記憶體級記憶體 需要利用 PCIe 5.0 和 PCIe 6.0 的高性能。 |

|

在汽車領域,目前的 ADAS(高級駕駛輔助系統)使用的是 PCIe 4.0,但未來的自動駕駛需要更高的性能來處理所有的攝像頭、雷達和雷射雷達收集到的資料。 |

|

AWS、Microsoft Azure 和 Google Cloud 等公司用於雲計算的超大規模資料中心可以充分利用所能獲得的所有頻寬,特別是實現主 CPU (Intel、AMD 或 Arm) 與加速器 (如NVIDIA GPU 或 Xilinx/ Intel FPGA) 之間的連接。 |

瞭解更多

請參閱 以下內容瞭解更多 PCIe 內容及 Cadence 為其提供的解決方案:

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」