減少因過孔 (via) 造成的寄生電容效應

自耦合電感補償使用在過孔(via)之設計,運用於高速信號環境,包含 30Gbps 頻帶寬度以上的數據傳輸率,這是個有效率並帶來效益的方法。運用這種方法可提高信號完整度,並能促進更多類型硬體的相互連接,比如處理器和記憶體之連接或處理器和各類網絡晶片之間。

電路板結構是由許多層銅箔電路疊加而成,電路層之間的信號通訊所經過的媒介的就是過孔(via)或稱為導孔。如果在由電路上過孔的功用上來看,過孔大致可分成兩種:一種用來連接各層間的電氣;第二是作固定器件或定位用。在製程上,有分為盲孔(blind via)、埋孔(buried via)和通孔(through via)。

過孔本身存在著寄生的雜散電容,此寄生電容會影響信號上升時間,減低了電路的速度。當過孔數量越來越多,產生的寄生電容效應也就越大。以往想要減少寄生效應產生的負面影響,通常都會在設計當中盡量選擇合理尺寸的過孔大小,例如 VCC 與 GND 的過孔,可以考慮使用尺寸較大的。另外一種方式則是使用較薄的 PCB 板,也可以減少寄生電容,或者是走線上盡量不要換層。

是否有更省時的方法來減少 Via 產生的電容效應,進而提升高頻時的速度? |

|

是否可以不用增加 Via 的尺寸,也可達到相同的電感補償機制? |

|

是否可以用較少的背鑽或埋孔來達到節省成本的目的? |

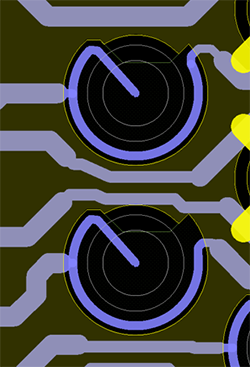

根據 Intel 在 2016 年時所申請的專利中,我們可以看到在走線準備要進入 Via 的階段時,在結構上做一些變化,設計成半圓形的走線進入 Via,通過 Via 之後可一樣設計成半圓形走線出來,這樣的做法可達到自耦合電感補償,增加電感效應,因為形狀酷似英文字母 G,我們稱之為 G-Shape Route。

現在藉由 GraserWARE 的 G-Shape Route 功能,就可以減少背鑽 (back drill) 或埋孔 (buried via) ,並輕鬆解決上述問題,大幅節省電路板製造的成本。

設計成 G 形的走線進入 Via

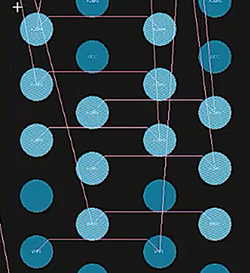

GraserWARE G-Shape Route 操作介面

Trace Layer:選擇要修改哪一層 |

|

Trace Width (WL,mils):設定走線寬度 |

|

Air gap trace to pad (LVia_gap,mils):設定走線與過孔之間的距離 |

|

Air gap pad to keepout (LVss_gap,mils):設定元件與禁制區域的距離 |

選擇好 Direction 之後,點選 ,可開始選擇需要更改的 PIN。

,可開始選擇需要更改的 PIN。

選擇完之後,點選右鍵 Finish